# TRACE32®

# **Product Overview**

## **Product Portfolio**

Lauterbach is the world's leading manufacturer of complete, modular microprocessor development tools with 35 years' experience in the field of embedded designs and has supported debugging and tracing of multicore chips for more than 10 years. It provides an integrated debug environment for embedded designs with its TRACE32 tools which consist of:

- PowerView, a universal GUI

- PowerDebug tools for debugging

- PowerTrace tools for program/data flow trace

- PowerIntegrator tools for logic analysis

- Software-only tools for debugging and tracing

### Introduction

Lauterbach TRACE32 tools support almost all common microprocessor architectures in use in the embedded market. The tools are designed around common modules which are universal and architecture independent. The tools play a very important role in the development of embedded systems and are used in the following ways:

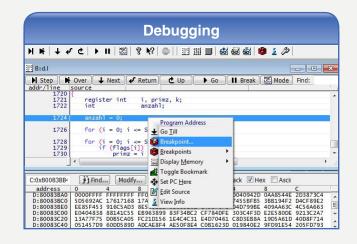

### Debug

Most cores for the embedded market provide access to on-chip debug features via a debug port. TRACE32 tools connect to this to control the core, access the data being processed by the core and provide developers with debugging over the embedded device: start, stop, step control; reading and writing memory and registers; setting breakpoints; tracking values of variables and so on. This means developers can diagnose software failures and memory corruption issues and correct the system to make it perform as expected.

### **Debug and Trace**

In many applications it is no longer enough to run a simple test on your code. In markets such as automotive, medical, aerospace and defence, it is increasingly necessary to prove how the code behaved under all possible conditions in real-time. This requires the tools to record the program flow information from the core via the integrated trace port of the processor. Both long-term and high-speed trace options are supported.

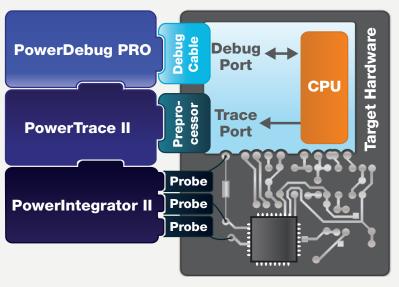

### Debug, Trace and Logic Analyzer

A debug system can be extended by adding a trace module or a logic analyzer. In some cases, both can be added to provide a very capable hard and software debug solution. Such a system can provide signal trace for logic analysis

and protocol analysis as well as correlating power usage to the code operation.

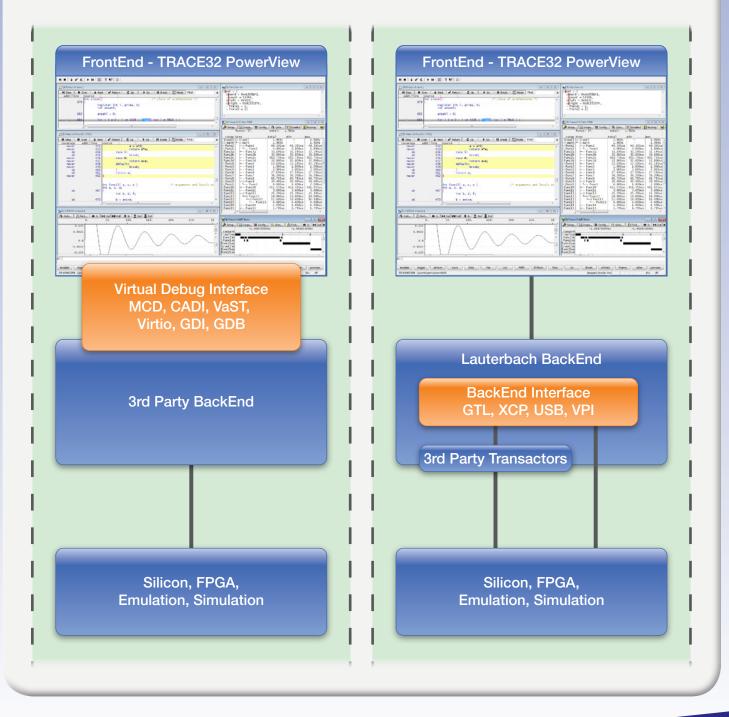

### Debug and Trace with Software-only Tools

Development is increasingly being undertaken in virtual targets, RTL simulators and emulators. As the technology and market leader of microprocessor development tools, Lauterbach is active in this development area, i.e. TRACE32 as a FrontEnd allows debugging and tracing of virtual prototypes as well as accessing emulation models via separate Back-End interfaces. Furthermore, Lauterbach is ready to support debugging solutions for native connections between host and target.

TRACE32 tools provide a comprehensive debug environment supporting all standard features and giving access to advanced on-chip debug features.

Listed below are the major functionalities provided by TRACE32 hardware tools.

### Debug

A debug system normally consists of a standard interface module and an architecture-specific debug cable providing standard debug features such as:

- JTAG, cJTAG, SWD and other debug interfaces

- Run control (program-/data-breakpoints, single stepping, real-time trigger)

- FLASH programming

- Multicore debugging

- OS-support with task analysis, UEFI

- HLL debugging (C, C++)

| Trace-based Code Coverage                              |          |             |      |     |

|--------------------------------------------------------|----------|-------------|------|-----|

| 🖉 Setup 🔃 🕰 Goto 🦉 List 🛛 🕂 Add 🛛 🔀 Load 🖓 Save 💿 Init |          |             |      |     |

| tree                                                   | coverage | executed 0% | 5 0% | 100 |

| ⊞ \jpeg                                                | partial  | 2.405%      |      |     |

| 🖂 \jdapimin                                            | partial  | 19.675%     | •    |     |

| jpeg_CreateDecompress                                  | never    | 0.000%      |      |     |

| jpeg_destroy_decompress                                | never    | 0.000%      |      |     |

| jpeg_abort_decompress                                  | never    | 0.000%      |      |     |

| Idefault_decompress_parms                              | never    | 0.000%      |      |     |

| jpeg_consume_input                                     | partial  | 39.873%     |      |     |

| jpeg_read_header                                       | partial  | 69.642%     |      |     |

|                                                        | partial  | 68.518%     |      |     |

| jpeg_has_multiple_scans                                | partial  | 74.074%     |      |     |

| jpeg_finish_decompress                                 | never    | 0.000%      |      |     |

| 🖃 \jquant2                                             | partial  |             |      |     |

| ⊞ prescan_quantize                                     | partial  | 13.000% -   |      |     |

| Ind_biggest_color_pop                                  | partial  | 15.517%     |      |     |

|                                                        | never    | 0.000%      |      |     |

| update_box                                             | partial  | 8.979%      |      |     |

| Image: median_cut                                      | partial  | 8.333% -    |      |     |

|                                                        | partial  | 28.915%     |      |     |

| select_colors                                          | never    | 0.000%      |      |     |

| find_nearby_colors                                     | partial  | 14.193%     |      |     |

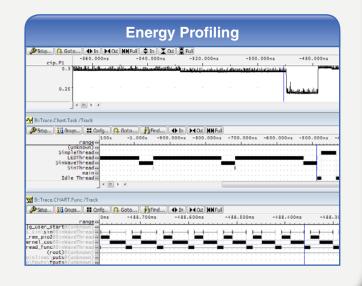

### Debug, Trace and Logic Analyzer

This system extends a debug/ debug and trace system with a logic analyzer module. The extra features provided are:

- Logic analyzer

- Protocol analyzer (USB, CAN, I2C, etc.)

- Energy profiling Time correlation with debug and trace tools

### **Debug and Trace**

A debug and trace system is composed of standard debug/trace modules and architecture-specific debug cables/trace probes (called preprocessors), which connect the base modules to the targets. In addition to the debug features it provides:

- Serial and parallel off-chip trace (ETM, Nexus, etc.)

- Non-intrusive flow trace

- Time-correlated multicore trace

- Run-time analysis and statistics

- Long-time trace (streaming)

- Code coverage

### **Product Characteristic**

Based on Lauterbach's modular concept, the hardware tools are composed of two parts: standard base modules and architecture-specific cables/probes. All base modules are completely universal and architecture-independent. The architecture-specific cables/probes connect the base modules and targets which enables the migration to new processor architecture by simply changing the cable/probe.

### **PowerView - The Universal GUI**

PowerView provides an integrated debug environment and a universal interface for the entire tool family. Menus, toolbars and dialog boxes offer intuitive and fast access to all debug, trace and logic analyzer features. It guarantees a consistent control for all tools and a coherent display of all software and hardware information required for debugging, tracing and further analysis. As a flexible user interface, PowerView allows developers to configure the environment to meet their specific needs. For example:

- Free selection of host interface and host OS

- Free selection of programming language and compiler

- Free selection of the OS on the target

- Free selection of the CASE tools

### **Debug Hardware Tools**

As debug information is provided by the on-chip debug interface, it becomes possible to test and analyze every aspect of the target operation including the bootstrap code, the target initialization, the interrupts, the drivers and the kernel. For OS types which dynamically load processes, a special detection mechanism is provided that catches the processor exactly on the entry point. This allows the developer to debug each process right from the start.

The debugger is available for all the common processors or SoCs on the embedded market. Since Lauterbach provide support for many kinds of cores, e.g. standard controller, DSPs, FPGA softcores and configurable cores, everything can be combined into a multicore chip and debugged with a TRACE32 debug tool.

# <image>

### Our range of products:

### PowerDebug USB 3

- USB 3.0 host interface

- Extensible with Logic Analyzers

### PowerDebug PRO

- USB 3.0 and Gbit Ethernet host interface

- Extensible with PowerTrace tools and Logic Analyzers

### **Debug and Trace Hardware Tools**

Real-time trace provides fast and systematic troubleshooting capabilities to detect complex errors that only occur under run-time conditions. The recorded and time-stamped program/data flow allows an overall analysis of the system performance as well as quality assurance features such as code coverage and cache analysis.

Over the last decades, Lauterbach has achieved world leading expertise for trace port protocols such as the Arm<sup>®</sup> Embedded Trace Macrocell<sup>™</sup> (ETM) and Nexus. Fast trace evaluation and analysis are guaranteed through advanced compression technologies and speed-optimized system software. With up to 4GB trace memory and the possibility of streaming to the host computer, a large amount of program and data flow information can be traced.

The preprocessor/Nexus adapter connects the realtime trace module to the standard trace port connector as defined by the silicon manufacturer. Lauterbach has developed custom hardware to meet the special needs of the different technologies. The AutoFocus II preprocessor's self-calibrating hardware ensures signal integrity up to 600Mbps per channel for parallel trace ports.

Lauterbach offers two products for high-speed serial trace ports: The Aurora HSSTP Preprocessor intended for low/mid trace bandwidth systems, and the future-safe PowerTrace Serial for systems with high trace bandwidth and for tracing via a PCIe 3.0 trace port.

### Our range of products:

### PowerTrace II and PowerDebug PRO

- 1 GB / 2 GB / 4 GB trace memory

- 17 logic analyzer channels

- Support for parallel trace ports up to 19.2 Gbit/s

- Support for serial trace ports up to 4 lanes, each lane max. 6.25 Gbit/s

### PowerTrace Serial and PowerDebug PRO

- 4GB trace memory

- Aurora based trace protocols up to 8 RX lanes

- PCIe 3.0-based trace protocol up to 8 RX/TX lanes

- Up to 12.5 GBit/s per lane

- 17 logic analyzer channels

# CombiProbe 2 and PowerDebug USB 3 or PowerDebug PRO

- Extended debug features

- Medium bandwidth trace up to 8 trace data channels

- 512 MB trace memory

- TRACE32 Streaming

### Add-on Hardware Logic Analyzer

The logic analyzer is designed as an integral part of the debug environment and fulfills the task of recording bus protocols, communication interfaces, interrupts and ports in order to analyze their timing. For instance the time relation between the program/data flow information sampled by the real-time trace and signals recorded by the logic analyzer can be viewed through the common IDE, PowerView.

PowerView provides ready-to-run software interfaces:

- To translate bus protocols into a program and data flow trace by using the common symbol database of the debugger.

- To perform various protocol analyses based on the raw data recorded for a communication interface.

The logic analyzer supports timing, state and transient recording. Simple and complex filters allow an optimized utilization of the trace memory. To analyze complex timing correlation, trigger conditions can be programmed to stop either the logic analyzer recording or the program execution at the precise point of interest.

### Our range of products:

### **PowerProbe**

- Up to 200MHz sampling rate

- 64 channels and 256K transient records

- Timing analyzer, pattern generator and pulse generator

### **PowerIntegrator**

- Up to 500MHz sampling rate (DDR)

- 204 channels and 512K transient records

### **PowerIntegrator II**

- Up to 500MHz sampling rate (DDR)

- 102 channels and 64M/128M/256M transient records

# µTrace<sup>®</sup> - Debug and Trace for Arm<sup>®</sup> Cortex<sup>®</sup>-M

The all-in-one debug and trace solution,  $\mu$ Trace, has been developed in response to the breakthrough of Cortex-M processors into the embedded market and targets the Cortex-M family specifically.

### **Characteristics**

- USB 3.0 interface to host computer

- 256 MByte trace memory

### **Software-only Tools**

Systems are becoming increasingly complex with more cores, peripherals, GPU and DSP integration and complex memory hierarchy. Tackling this complexity with system level validation from the early stages of product development on virtual prototypes, RTL simulators and emulators helps engineers to avoid potential problems that might otherwise surface only after tape-out.

Therefore, debugging of virtual prototypes is becoming an important feature. Lauterbach has been working closely with semiconductor design companies and leading EDA partners to provide debugging and trace solutions for pre-silicon hardware and software development and validation.

TRACE32 controls the virtual prototype via the universal GUI PowerView as FrontEnd and accesses the simulator and emulator models via a separate Back End interface. The experience and knowledge originating from developing hardware debugging tools has flowed into the development of software-only tools, which ensures the development efficiency and endows the products with high quality, reliability and universality. For example the scripts generated for the virtual targets can be reused later on for the real targets.

7

# **TRACE32**<sup>®</sup> Support for all project phases

Lauterbach GmbH Altlaufstraße 40 • 85635 Höhenkirchen • Tel: +49 8102 9876 0 • sales@lauterbach.com Visit our official Youtube channel and discover our tutorials: http://www.youtube.com/user/lauterbachgmbh

x20.3